# IP Core Protection using Voltage-Controlled Side-Channel Receivers

Peter Samarin<sup>1,2</sup>, Kerstin Lemke-Rust<sup>1</sup>, and Christof Paar<sup>2</sup>

Bonn-Rhein-Sieg University of Applied Sciences<sup>1</sup> Ruhr-Universität Bochum<sup>2</sup> Germany

Bonn-Rhein-Sieg University of Applied Sciences

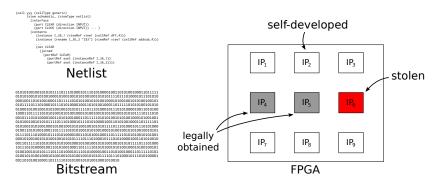

#### IP Protection on FPGAs

- How to detect illegally used cores in the field?

- Challenges

- Bitstreams are encrypted

- IP cores are parts of larger systems

## IP Protection using Side-Channels

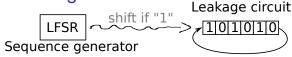

#### Verification

- Measure the power consumption

- Correlate the known LFSR sequence to the measurement

(Becker et al., 2010)

May 4, 2016

#### Our Contribution

- Establish an input side channel to individual IP Cores using voltage modulation

- (Sun et al., 2011) used temperature (several bits/s)

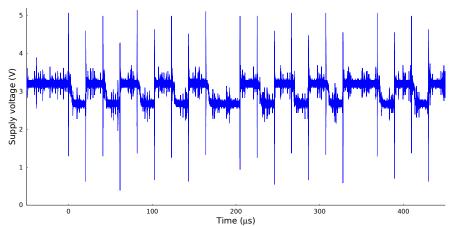

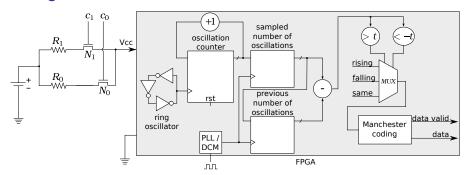

### Voltage-Based Side-Channel Receivers

- Supply voltage control

- 3 Voltage levels: V<sub>reset</sub>, V<sub>0</sub>, V<sub>1</sub> (V<sub>2</sub> is not used)

- Detection of changes in supply voltage

- Ring oscillator sampled by a fixed clock

- Relative threshold to find rising and falling edges

- Manchester coding

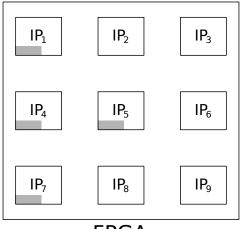

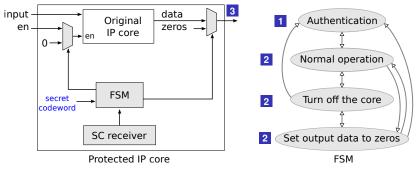

#### **IP** Protection

**FPGA**

- Embed an SC-receiver into each protected IP core

- Send commands to protected IP cores

#### Verification

- Send a core-dependent secret codeword

- 2 Send commands, observe the behavior of the chip:

- Turn off the core

- Set output data to zeros

- Return to normal operation

- Deselect core

- If the behavior is unusual then stop, else goto step 2

May 4, 2016

**Experimental Setup**

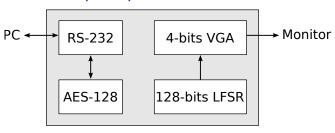

## A Proof-of-Concept Implementation

- Digilent board with a Spartan 3 (XC3S200) FPGA<sup>1</sup>

- 50MHz external clock

- Voltage control by a breadboard circuit

- Voltage levels V<sub>reset</sub> = 0V, V<sub>0</sub> = 2.8V, V<sub>1</sub> = 3.2V

- Transmission rate 2.4 KBits/s

- 32-Bit codewords

<sup>&</sup>lt;sup>1</sup>http://store.digilentinc.com/spartan-3-board-retired/

## The Price to Pay

| Codeword size (bits) | N. of slices |

|----------------------|--------------|

| 32                   | 49           |

| 64                   | 70           |

| 80                   | 81           |

| 128                  | 111          |

- Need to try several codewords (in the worst case all)

- Cannot measure once and try them all just on the data

- Cores without clock cannot be protected

- More recent work on SASEBO-GII board<sup>2</sup>

- Spartan 3 FPGA for control

- Virtex 5 (XC5VLX50) FPGA for measurements

- Same breadboard circuit didn't work (voltage regulator)

<sup>&</sup>lt;sup>2</sup>http://satoh.cs.uec.ac.jp/SASEBO/en/board/sasebo-g2.html

## Summary and Future Work

- Voltage-controlled side-channel receiver on FPGAs

- IP protection of individual cores

- Strong proof of IP ownership

- Other applications

- Hardware trojans triggered by a codeword

- Protection against counterfeits

- Future work

- Testing other FPGAs and boards

- Adressing voltage regulators

- Two-way side-channel communication

#### References

Becker, G., Kasper, M., Moradi, A., and Paar, C. (2010). Side-channel based watermarks for integrated circuits. In *Hardware-Oriented Security and Trust (HOST), 2010 IEEE International Symposium on*, pages 30–35.

Sun, J., Bittner, R., and Eguro, K. (2011). FPGA side-channel receivers. In *Proceedings of the 19th ACM/SIGDA International Symposium on Field Programmable Gate Arrays*, FPGA '11, pages 267–276, New York, NY, USA. ACM.